- 您现在的位置:买卖IC网 > Sheet目录299 > 71M6543F-IGT/F (Maxim Integrated Products)IC ENERGY METERING

�� �

�

�

�71M6543F/71M6543G� Data� Sheet�

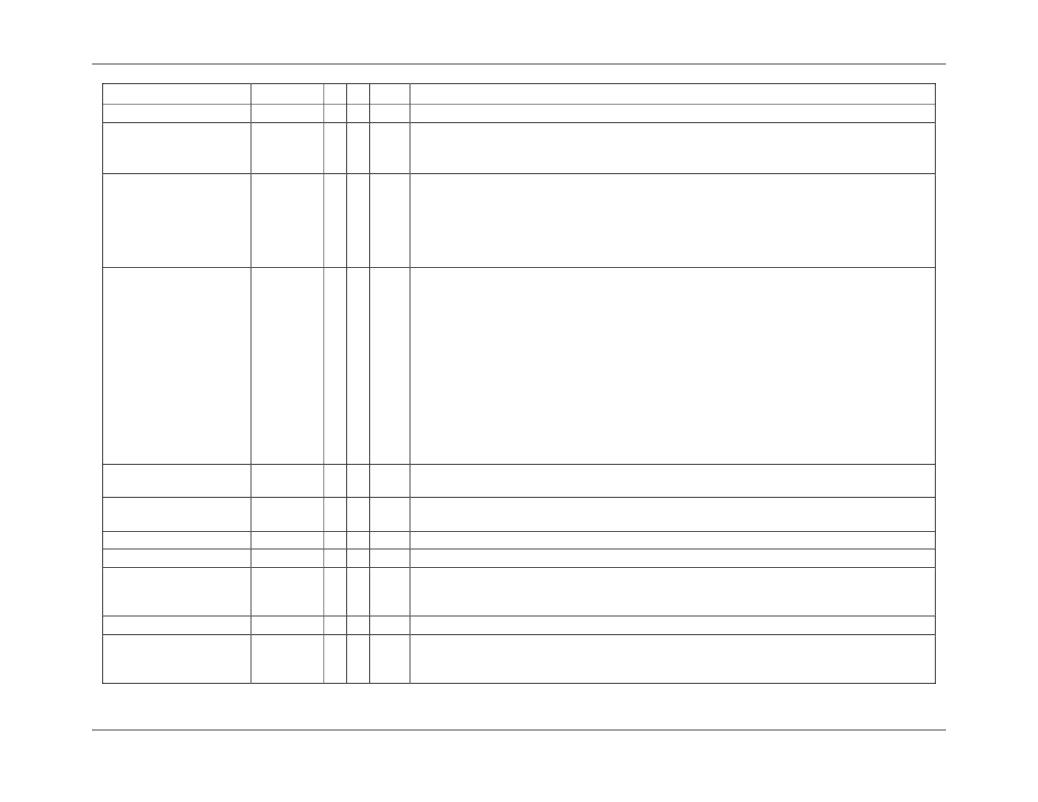

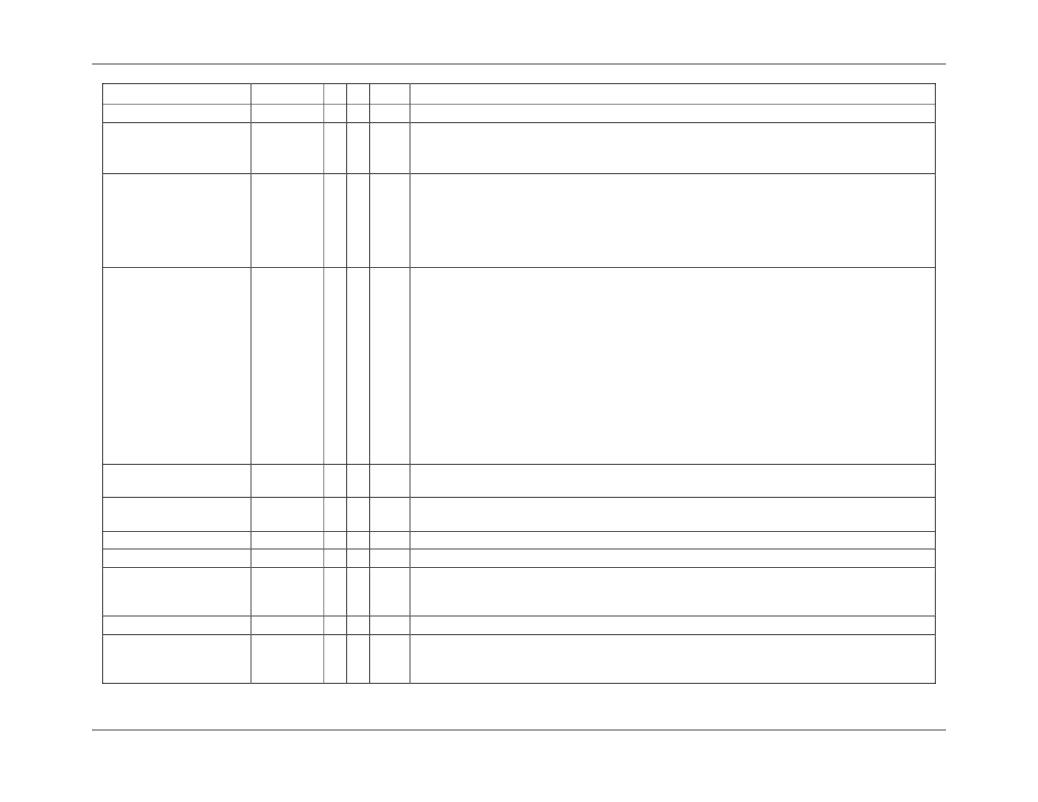

�Name�

�Location� Rst Wk� Dir�

�Description�

�PLL_OK�

�PLL_FAST�

�SFR� F9[4]�

�2200[4]�

�0�

�0�

�0�

�0�

�R�

�R/W�

�Indicates� that� the� clock� generation� PLL� is� settled.�

�Controls� the� speed� of� the� PLL� and� MCK.�

�1� =� 19.66� MHz� (XTAL� *� 600)�

�0� =� 6.29� MHz� (XTAL� *� 192)�

�PLS_MAXWIDTH[7:0]�

�210A[7:0]� FF� FF� R/W�

�PLS_MAXWIDTH[7:0]� determines� the� maximum� width� of� the� pulse� (low-going� pulse� if�

�PLS_INV� =0� or� high-going� pulse� if� PLS_INV� =1).� The� maximum� pulse� width� is�

�(2*� PLS_MAXWIDTH[7:0]� +� 1)*T� I� .� Where� T� I� is� PLS_INTERVAL[7:0]� in� units� of� CK_FIR�

�clock� cycles.� If� PLS_INTERVAL[7:0]� =� 0� or� PLS_MAXWIDTH[7:0]� =� 255,� no� pulse�

�width� checking� is� performed� and� the� output� pulses� have� 50%� duty� cycle.� See� 2.3.6.2�

�VPULSE� and� WPULSE� .�

�PLS_INTERVAL[7:0]�

�PLS_INV�

�PORT_E�

�PRE_E�

�PREBOOT�

�210B[7:0]�

�210C[0]�

�270C[5]�

�2704[5]�

�SFRB2[7]�

�0�

�0�

�0�

�0�

�–�

�0�

�0�

�0�

�0�

�–�

�R/W�

�R/W�

�R/W�

�R/W�

�R�

�PLS_INTERVAL[7:0]� determines� the� interval� time� between� pulses.� The� time� between�

�output� pulses� is� PLS_INTERVAL[7:0]� *4� in� units� of� CK_FIR� clock� cycles.� If�

�PLS_INTERVAL[7:0]� =� 0,� the� FIFO� is� not� used� and� pulses� are� output� as� soon� as� the� CE�

�issues� them.� PLS_INTERVAL[7:0]� is� calculated� as� follows:�

�PLS_INTERVAL[7:0]� =� Floor� (� Mux� frame� duration� in� CK_FIR� cycles� /� CE� pulse� updates� per� Mux�

�frame� /� 4� )�

�For� example,� since� the� 71M6543� CE� code� is� written� to� generate� 6� pulses� in� one� integration�

�interval,� when� the� FIFO� is� enabled� (i.e.,� PLS_INTERVAL[7:0]� ≠� 0)� and� that� the� frame�

�duration� is� 1950� CK_FIR� clock� cycles,� PLS_INTERVAL[7:0]� should� be� written� with�

�Floor(1950� /� 6� /� 4)� =� 81� so� that� the� five� pulses� are� evenly� spaced� in� time� over� the�

�integration� interval� and� the� last� pulse� is� issued� just� prior� to� the� end� of� the� interval.� See�

�2.3.6.2� VPULSE� and� WPULSE� .�

�Inverts� the� polarity� of� WPULSE,� VARPULSE,� XPULSE,� and� YPULSE.� Normally,� these�

�pulses� are� active� low.� When� inverted,� they� become� active� high.�

�Enables� outputs� from� the� SEGDIO0-SEGDIO15� pins.� PORT_E� =� 0� blocks� the� momentary�

�output� pulse� that� occurs� when� SEGDIO0-SEGDIO15� are� reset� on� power-up.�

�Enables� the� 8x� pre-amplifier.�

�Indicates� that� pre-boot� sequence� is� active.�

�RCMD[4:0]�

�SFR� FC[4:0]� 0�

�0�

�R/W�

�When� the� MPU� writes� a� non-zero� value� to� RCMD� ,� the� 71M6543� issues� a� command� to�

�the� appropriate� remote� sensor.� When� the� command� is� complete,� the� 71M6543� clears�

�RCMD.�

�RESET�

�RFLY_DIS�

�2200[3]�

�210C[3]�

�0�

�0�

�0�

�0�

�W�

�R/W�

�When� set,� writes� a� one� to� WF_RSTBIT� and� then� causes� a� reset.�

�Controls� how� the� 71M6543� drives� the� power� pulse� for� the� 71M6xxx.� When� set,� the�

�power� pulse� is� driven� high� and� low.� When� cleared,� it� is� driven� high� followed� by� an� open�

�circuit� fly-back� interval.�

�v2�

�111�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

71M6545-IGT/F

IC ENERGY METERING

720-10007-00300

CBL D-SUB 9PIN FMAL-25PIN FML 3M

720-10010-00025

CBL DSUB 9PIN FML-25PIN MAL .25M

720-10020-00300

CBL DSUB 9PIN FML-9PIN MALE 3M

720-10021-00300

CBL DSUB 9PIN FML-9PIN FEMAL 3M

72231-0881

8 POS T/P SHLD 4 GR ASSY

7250B

PANEL KIT BOTTOM FOR R-1220 CASE

731-10061-00200

CBL DSUB HD 15FEMAL-15MALE 2.0M

相关代理商/技术参数

71M6543F-IGTR/F

功能描述:计量片上系统 - SoC Precision Energy Meter IC

RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel

71M6543FT-IGT/F

制造商:Maxim Integrated Products 功能描述:ENERGY METER ICS - Rail/Tube

71M6543FT-IGTR/F

制造商:Maxim Integrated Products 功能描述:3-PHASE SOC, 64KB FLASH, PRES TEMP SENSOR - Tape and Reel

71M6543G

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Selectable Gain of 1 or 8 for One Current Energy Meter ICs Metrology Compensation

71M6543GH

制造商:未知厂家 制造商全称:未知厂家 功能描述:电表IC

71M6543GHT-IGT/F

制造商:Maxim Integrated Products 功能描述:3-PHASE, 128KB, PRES TEMP SENSOR, HI PREC - Bulk

71M6543GHT-IGTR/F

制造商:Maxim Integrated Products 功能描述:3-PHASE, 128KB, PRES TEMP SENSOR, HI PREC - Tape and Reel

71M6543G-IGT/F

功能描述:计量片上系统 - SoC Precision Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel